数据输出电路的优化基理方案解析1 引 言在LED大屏幕等显示系统对数据输出速度的要求日益提高的背景下,当前对控制设备进行改造的过程中,首选的办法是更换更高速率的微处理器,而对硬件电路的挖潜往往容易被忽视。在实践运用中,建议应先考虑

图1(c)所示为LDO的多种应用,它可以是标准电源、电池管理应用、开关转换后调节器及多输出配置等。

LDO的应用例举(见图1(d) )所示。更细小的双路低压差线性稳压器MAX8530(见图1(d) )所示,可安装于下1.8mm×1.8mm,为超晶片级封装(UCSP)为蜂窝电话、PDA和数码相机节省80%空间,100mV低压差(于 100mA),200mA单输出。因到2005年底时,CM0S LenS(透镜)的像素提高到5M-10M以上,因而中高档的DSC方案纷纷采用,CMOS Lens需要有三组不同电压的电源,如1.8V和2.8V,电流在100mA-150mA,所以用双MAX8530LDO是比较适宜(见图1(e) )。

需要说明的是,由于供电电源一般功率电感器公司情况下往往是锂离子电池,因此在输出电压低于3.3V时降压转换器可以提供更高的效率。但是,对于某些电源电压而言,使用LDO更为合理。用于在处理器中产生内部时钟信号的锁相环(PLL)对任何噪声都很敏感。因此,需要采用LDO为处理器的该部分供电。由于该区块的电流一般为5mA-30mA,因此对整体效率的影响较小。实时时钟(RTC)的供电也同样如此。如果用接近 于输出电压的电压为LDO供电,则LDO就是一种名副其实的简单、低成本、高效率解决方案。在采用 1.8V I/O电压的应用中,可以通过该电压轨为PLL-LDO供电,从而使其输出电压达到1.3V,效率达到72%。

于输出电压的电压为LDO供电,则LDO就是一种名副其实的简单、低成本、高效率解决方案。在采用 1.8V I/O电压的应用中,可以通过该电压轨为PLL-LDO供电,从而使其输出电压达到1.3V,效率达到72%。

3、DC/DC特征与应用

3.1 DC/DC特征

*当输入与输出的电压差较高时,开关稳压器避开了所有线性稳压器的效率问题。它通过使用低电阻开关和磁存储单元实现了高达96%的效率,因此极大地降低了转换过程中的功率损失。

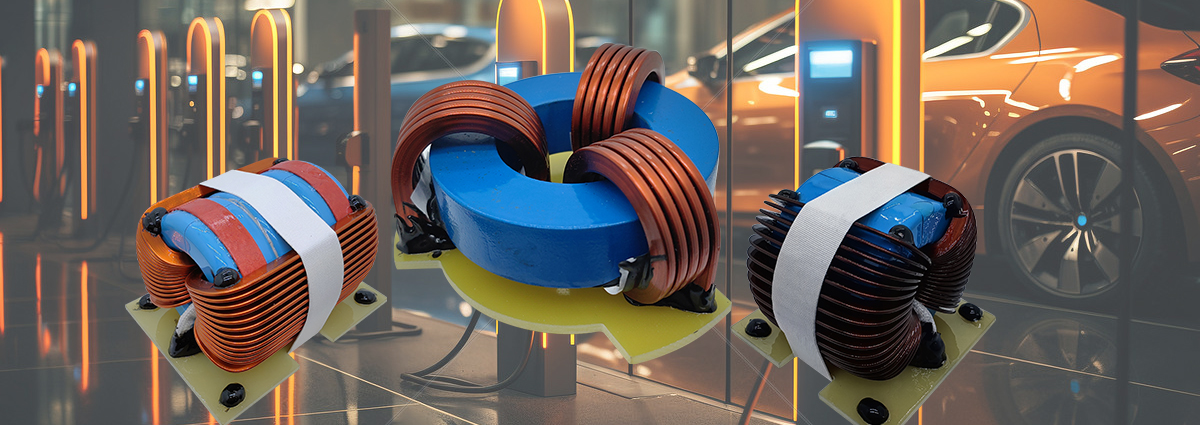

*选用开关频率高的DC/DC可以极大地缩小外部功率电感器和电容器的尺寸和容量,如超过2MHz的高开关频率。

*开关稳压器的缺点较小,通常可以用好的设计技术来克服。但是电感器的频率外泄干扰较难避免,设计应时对其EMI幅射需要考虑。

3.2 DC/DC(Buck)应用电路设计与应用插件电感器生产商Layout的设计技巧

图2(a)为DC/DC(Buck)应用电路设计方案,图中粗线是大电流的通道,应选用MuRata,Tayo-yuden,Tdk&AVX品质优良、低ESR’X7R&X5R陶瓷电容器。

DC/DC(Buck)应用Layout的设计技巧-PCS扳没计要点

要得到一个运作稳定和低噪音的高频开关稳压器,需要小心安排pcb板的布局结构,所有的器件必需靠近DC/DC,可以把PCB按功能分成几块,如图所示:保持通路在Vin、Vout之间,Cin、Cout接地很短:以降低噪音和扰;R1、R2和CF的反馈成份必须保持靠VFB反馈脚;大面积直接联接 2脚和Cin、Cout负端。

图2(b)为应用于MCU/DSP内核供电示意图