功率电感:有源电感设计理论及方法 1 有源电感实现的基本原理 有源电感的电路结构有多种形式,其广泛应用的基本结构是:采用回转器和电容组成。回转器具有将一个端口上的电压回转为另一个端口上的电流的性质。利用这种性质,晶体管的寄生电容或外

在《电源设计小贴士 40:非隔离式电源的共模电流》中,我们讨论了开关级中大电压摆动如何形成共模电流的问题,并介绍了它驱动电流进入电容到机架接地的过程。

在这篇《电源设计小贴士》中,我们将继续讨论共模电流的问题。

在隔离式电源中,这种情况变得更加糟糕,因为隔离变压器的次级绕组最终连接至机架接地。

因此,存在相当大的初级到次级寄生电容。

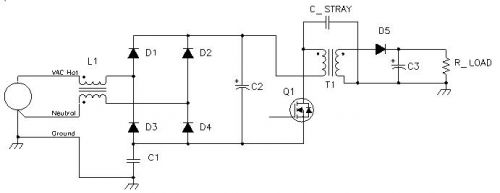

图 1 显示了一个这种情况的简化示意图。

图 1 Q1 高压开关驱动 C-STRAY 中共模电流

这是一种离线工作的隔离式反向结构。

110 伏到 220 伏 AC 输入电源经过整流,从而向功率级提供 100 伏到 400 伏DC。

电源开关迅速开启和关闭,在 Q1 漏极上产生 500 伏到 600 伏开关波形,其同时也施加于电源变压器的初级绕组。

这种开关电压,在变压器初级绕组到次级绕组之间的杂散电容中形成电流。

该电流流经负载的预设机架接地,或者只是以电容方式接地耦合。

该电流必须完成噪声返回通路,从而产生开关式电源。

在没有 C1 的情况下,它流回 AC 输入电源,然后流入电源的输入线,其很可能会超出 EMI 辐射规格。

由于其高电源阻抗,这种电流的滤波特别困难。

变压器的杂散电容大小级别为 100 pF,其典型电源开关频率的阻抗为 10 千欧。

只在电流通路中添加一个电感来减小这种电流的方法并不实际。

例如,如果我们希望将电流减小 10 倍,其要求100 千欧的电抗(也即 0.1 亨),且分布电容小于 10 pF,这并不现实。

电容器 C1 带来了另一种解决方案。

它为电流提供了一条本地返回通路。

大多数共模电流通过该电容器在电源内部回流,而不是通过 AC 输入电源回流。

另外,C1 还减小了系统的电源阻抗,这样共模串联电感 L1 就变得现实了。

在共模滤波器的设计过程中,一个关键因素是 C1 值的选择。

从电磁干扰 (EMI) 的角度来看,其值越大越好。

更大的电容可获得更小的 EMI 信号,且电源阻抗也更低。

你可以利用电容的平方原则,估计 EMI 信号的减小程度。

但是,高电容也意味着机架连线的线频率电流更大。

另外,这种电流还有一些安全限制,目的是减少触电事故的发生机率。

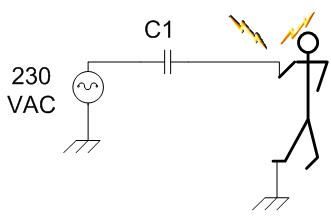

当电源机架连线断裂时,人员进入电流通路便会发生触电事故,如图 2 所示。

IEC Std 601-1 将这种电流的大小限制为 0.5 mA RMS,同时人们还在讨论出台更为严格的安全规定。

输入为 230 伏时,IEC 可有效地将 C1 值限制为 4700 pF。

图 2 C1 可以成为一种触电风险

总之,驱动寄生电容机架接地的高 dV/dt 电压波形,会形成共模电流。

这种电流特别难以滤波,原因是其存在高电源阻抗。

滤波要求使用一个机架电容器,提供另一条本地返回通路,并降低阻抗。

尽管从 EMI 滤波器的角度来看,电容越大越好,但是总电容受限于安全规定。

如欲了解本文的更多详情,敬请参阅 2003 Unitrode 电源设计研讨会主题 3:www.ti.com/2003powerseminar-ca。

下次,我们将讨论如何利用共模滤波电感器在离线电源中实现共模滤波,最终达到减少 EMI 的目的。

深入阅读: 电源设计小贴士46:正确地同步降压FET时序 电源设计小贴士43:分立器件——一款可替代集成MOSFET驱动器的卓越解决方案 [视频]电源设计小贴士32和33:注意SEPIC耦合电感回路电流 电源设计小贴士38:使用简易锁存电路保护电源 电源设计小贴士 40:非隔离式电源的共模电流 电源设计小贴士 41:DDR内存电源 [视频]电源设计小贴士31:同步降压MOSFET电阻比的正确选择

立即加入德州仪器技术社区