利用Virtex-5 FPGA实现最低功耗过渡至65纳米工艺的FPGA具备采用更小尺寸工艺所带来的优势:低成本、高性能和更强的逻辑能力。尽管这些优势能够为高级系统设计带来激动人心的机会,但65纳米工艺节点本身也带来了新的挑战。例如,在为产品选

摘要:采用交叉耦合结构,利用TSMC90nm 1P9M 1.2V RFCMOS工艺设计的全集成LC压控振荡器(VCO),符合IEEE 802.1lb/g WLAN通信标准。调谐电压为0~1.2V,具有150MHz的调谐范围(2.44GHz~2.59GHz)。利用Mentor Graphics Eldo对该电路进行仿真,仿真结果显示,在2.5GHz工作频率处,相位噪声约为-122.3dBc/Hz@1MHz,功耗仅为1.9mW。

关键词:压控振荡器;无线局域网;低压;低功耗;低相位噪声

0 引言

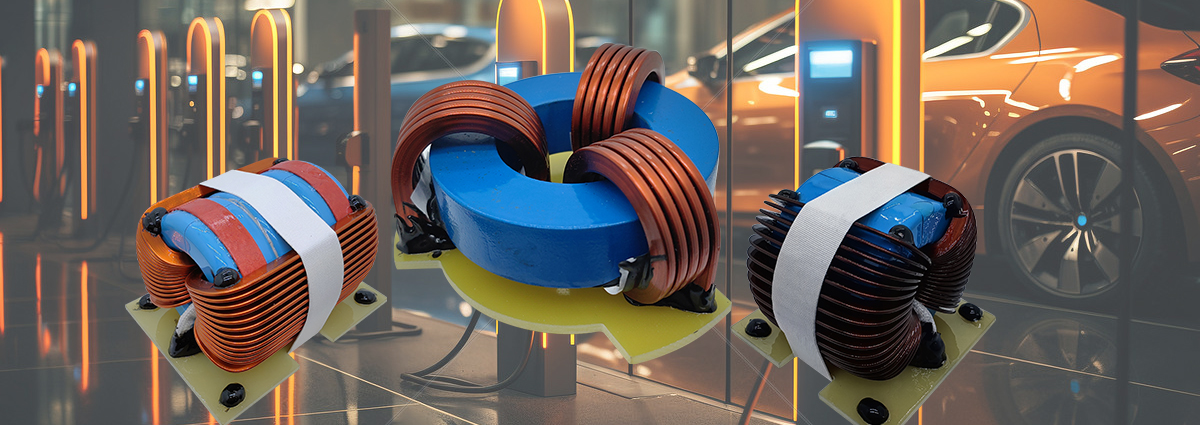

随插件电感着便携式无线设备市场的迅速扩张,降低系统功耗成为射频集成电路设计的重要方向。降低电源电压作为减小电路功耗的一种常规方法,效果十分明显,但设计时必须面对输出摆幅下降、信噪比恶化,以及系统对PVT(Process,Voltage,Temperature)因素更加敏感等诸多问题。

压控振荡器(VCO)作为频率合成器的关键模块,其稳定性和频谱纯度对通信收发系统的性能至关重要。如何在输出摆幅、相位噪声、调谐范围、偏置电流和功耗之间取得较好的折衷是VCO设计的最大难点。本文在总结LC VCO一般性设计方法和理论的基础上,设计了一个适用于IEEE 802.11b/g WLAN(无线局域网)通信标准的VCO。为降低功耗,该VCO采用TSMC 90nm 1.2V低电源电压工艺,仿真结果显示,在2.5GHz中心频率处,功耗仅为1.9mW,相位噪声约为-122.3dBc/Hz@1MHz,相比其它文献的同中心频率VCO设计,功耗更低,同时具有较低的相位噪声。

1 LC VCO的基本工作原理

交叉耦合型LC VCO利用有源器件-g,不断补充LC谐振同路寄生电阻g所消耗的能量,以维持振荡。有源器件一般可用MOS对管构成的负阻实现,为确保振荡,需满足条件

其中,αg为增益裕度系数,典型值取2~3。gtank为LC谐振回路等效导纳,gactive为负阻导纳,且有

交叉耦合MOS管跨导可表示为

相对单NMOS或PMOS交叉结构VCO而言,互补交叉结构VCO的输出波形更对称,噪声特性更好。因此本文选择互补交叉结构的VCO,电路拓扑结构如图1所示。根据LC振荡器基本理论,该VCO的输出频率为

其中,Ctotal为VCO的总电容值,包括固定电容Cfix、可变电容Cv,以及寄生电容Cp(电感L、交叉耦合MOS管和后级电路的寄生电容),调谐电压Vtune控制Cv,使VCO输出频率厂f0随Vtune的变化而变化。

2 电路设计

2.1 片上电感L的选取

相位噪声与Q值平方成反比关系,LC谐振回路的Q值越高,VCO相位噪声越小。片上电容的品质因数比片上电感大很多,因而LC谐振回路的品质因数主要取决于片上电感。由于片上电感器市场电感和硅衬底之间存在耦合电容,能量将被耦合至衬底中,导致能量损耗,因此极大降低了片上电感的品质因数Q值。片上电感Q值可通过测量电感的Y参数获得:

TSMC 90nm 1P9M 1.2V RFCMOS工艺的扁平型电感片上电感为铜金属八边形平面螺旋电感,制作在P型衬底上。为降低电感与衬底间的氧化工字电感层电容,减小高频损耗,通常使用工艺中最厚的顶层金属制作电感。TSMC 90nm 1P9M 1.2VRFCMOS库中的片上电感采用Ultra Thick Metal工艺,位于顶层金属M9层,共分三种类型:标准型(STD)电感、对称型电感(SYM)和带中心抽头的对称型电感(SYMCT),可调节的参数包括电感金属线宽度w、电感金属线圈数nr和电感内直径rad。为获得更高的品质因数,应取最大的金属线宽w,以减小寄生电阻。对不同规格的电感进行S参数的扫描仿真,经计算比较后,最终采用尺寸为w=15 μm,nr=3,=90 μm,感值L=1.43nH的SYM电感,在振荡频率2.5GHz处,其Q值约为14.9。

2.2 负阻RFMOS管的选取

RFPMOS和RFNMOS对管构成负阻单元,提供维持振荡所必须的能量。由式(1)~(3)可知,W/L必须足够大以确保起振。当gmp=gmn时,输出波形具有最好的对称性,可有效抑制1/f噪声的上变频。由于电子的迁移率是空穴的2~3倍,故RFPMOS管和RFNMOS管的W/L比应在2~3之间。为降低振荡器功耗,并减小MOS管的寄生电容,RFNMOS管应取工艺允许的最小尺寸,即nr×l×w=11×0.1μm×1μm。仿真结果表明,RFPMOS管尺寸取RFNMOS管的3倍时,输出波形具有最好